Fpga Design Flow Using Eda Tools

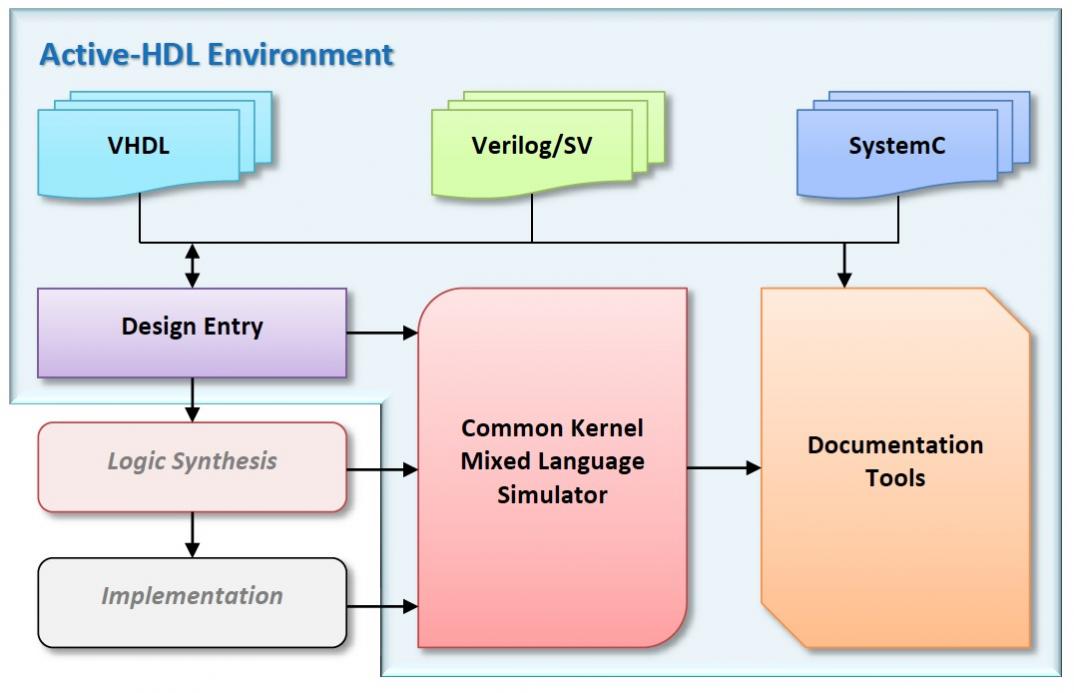

I've used FPGA vendor-supplied tools from both Xilinxand Lattice Semibefore, so I wanted to see what EDA tools Aldec has to offer for FPGA design. I read the Aldecwhite paper, Corporate Standardization of FPGA Design Flow, and summarize what I found.

Here's the big picture of using Aldec tools (shown in light blue) in a Windows-based flow along with FPGA vendor tools (logic synthesis, implementation – Place & Route):

Design Entry

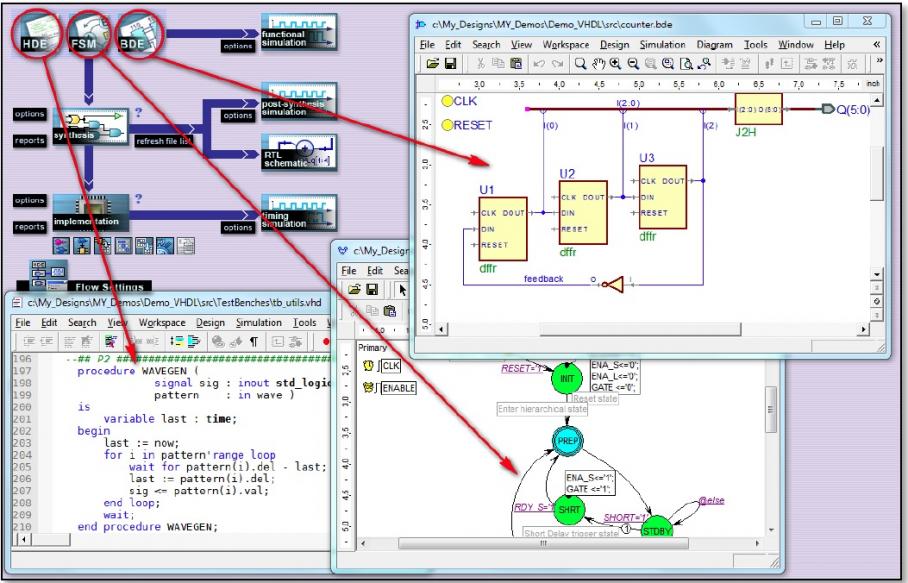

You have three ways to do design entry:

- Coding with HDL Editor

- Graphically with the Block Diagram Editor

- Graphically with the Finite State Machine Editor

If you come from the schematic capture world then the Block Diagram Editor looks familiar and supports hierarchy. Finite State Machines (FSM) are intuitive to enter and debug graphically, then get auto converted into the language you choose. Software-oriented engineers will be attracted to the HDL Editor with its color-coding, linting and language assistant for templates.

Code from the HDL Editor can become a block, and you can even convert code into an FSM diagram.

RTL Verification

Design entry goes relatively quickly for FPGA designs, while most of your design effort is spent in verification of the RTL so that it meets specs and functions correctly. Your RTL code is linted for correctness prior to simulation or logic synthesis, reducing the number of dynamic simulations required.

Testbenches are used to define both stimulus and expected functional response. You can hand-code a testbench or auto-generate with a Wizard, saving you time typing.

Debugging simulation is both text-based and graphical with waveforms using the simulator. You can set breakpoints in the simulation at a line of code, or when a condition occurs (signal event, transaction, values).

There's analysis for code coverage of your dynamic simulations showing:

- Statement coverage

- Branch coverage

- Path coverage

- Expression coverage

- Toggle coverage

When trying to debug why something happened in simulation use the Advanced Dataflow window to identify the source.

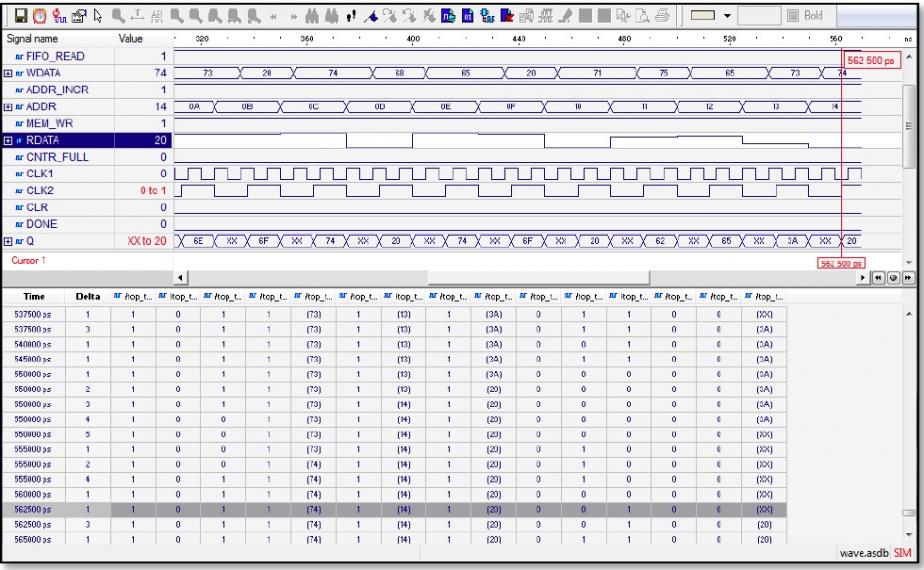

The waveform viewer is often using in simulation and debug to show signals and buses graphically or in text form.

When your RTL code has two-dimensional array types then use the Memory Viewer to debug the contents.

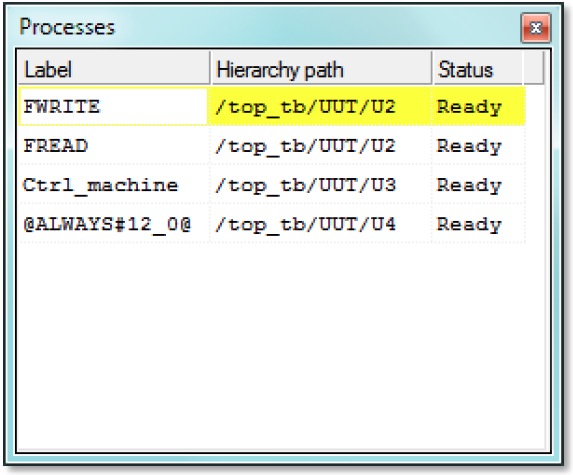

Processes in your VHDL or Verilog code can be debugged with a Process Window.

Intellectual Property (IP) can be protected in your design by using compiled models and then distributing them a library files, thus protecting your source code.

Anything that you design or simulate in Active-HDL can be saved using the popular PDF or HTML output formats, making your documentation job easier.

Logic Synthesis

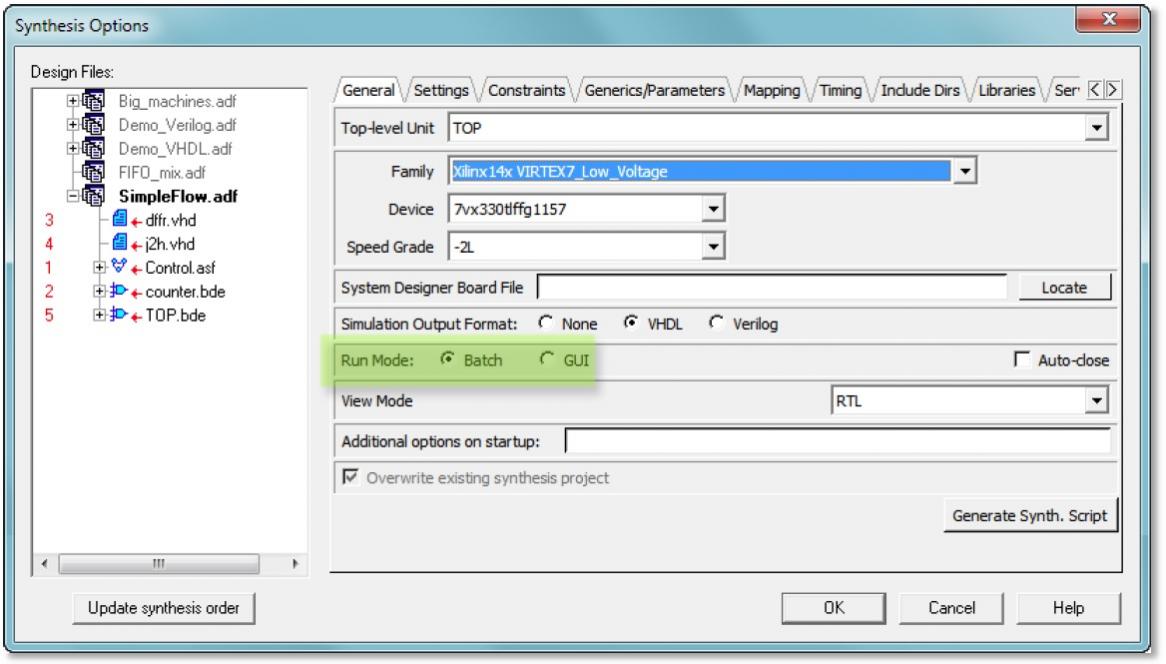

You can launch logic synthesis in either GUI or batch modes, depending on how large the block size is, and Active-HDL supports all the popular logic synthesis or place and route tools. The logic synthesis output is an EDIF netlist, ready for use by place and route.

Gate-level Verification

The EDIF netlist from logic synthesis can be simulated against the testbench you created earlier during design entry to verify correct functionality.

Implementation (Place and Route)

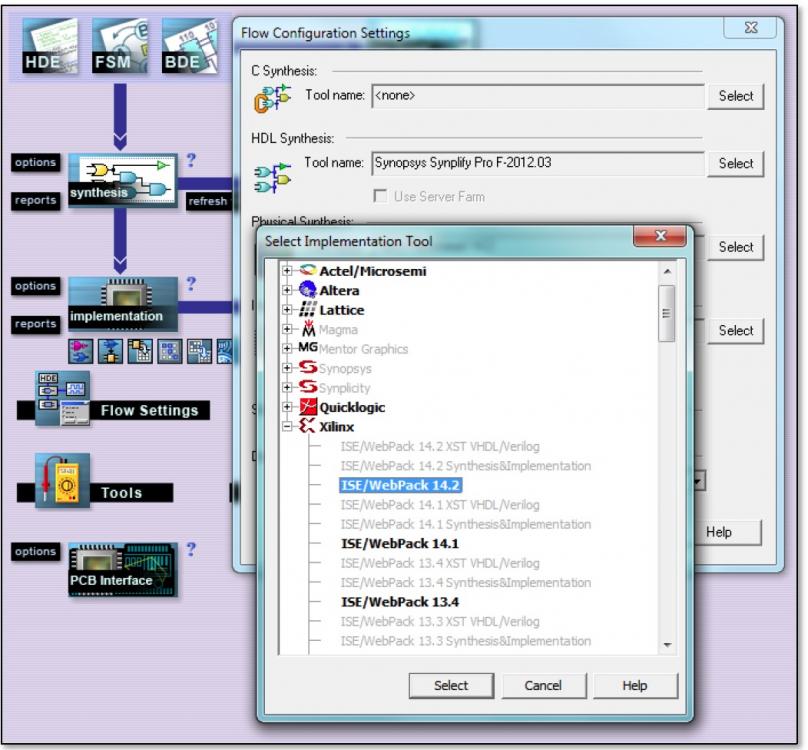

Again you get to choose running Place and Route in GUI or batch mode, along with selecting a specific FPGA vendor device.

Timing Simulation

After Place and Route we have the exact interconnect delays and can do a final timing simulation be re-using our original testbench created at design entry. If there's a timing violation then you'll see it graphically in the waveform viewer and can then start debug.

Summary

Aldec has capable Windows-based EDA tools for FPGA design: Design Entry, RTL Verification, Gate & Timing Verification. If you tend to use multiple FPGA vendors, then using Active-HDL could save you some time as a common set of EDA tools across all FPGA designs. Linux-based EDA tools from Aldec are called Riviera-PRO.

For more details read the 12 page white paper, Corporate Standardization of FPGA Design Flow.

Share this post via:

Fpga Design Flow Using Eda Tools

Source: https://semiwiki.com/eda/aldec/1867-an-fpga-design-flow-with-aldec-tools/

Posted by: murphyroyshe.blogspot.com

0 Response to "Fpga Design Flow Using Eda Tools"

Post a Comment